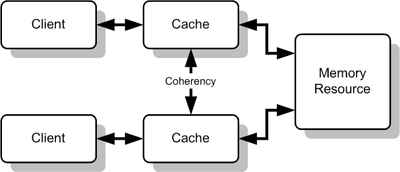

Vahemälu sidusus (cache coherence) tähendab meetmete ja reeglite kogumit, mis tagavad, et sama füüsilise mäluadressi koopiad eri vahemäludes sisaldavad kooskõlalisi ja mõistlikke andmeid. Vahemälu kasutatakse selleks, et parandada juurdepääsu kiirust mäluressurssidele, kuid kui samale ressursile on mitu vahemälu (näiteks mitme tuumaga protsessoris või jaotatud süsteemis), võivad tekkida olukorrad, kus ühe koopia muutmine ei peegellu teistes koopiates. See võib viia programmi vale käitumiseni, kui tuumad/klientprogrammid loevad vananenud andmeid.

Probleeme võib tekkida, kui ühise mäluressursi vahemälu on palju: vahemälus olevad andmed ei pruugi enam olla ajakohased või eri vahemälud võivad sisaldada erinevaid väärtusi samal mälublokil. Tavaline näide on protsessorite vahemälu mitme protsessoriga süsteemis. Kui ühel kliendil (tuumal) on mälubloki koopia eelmise lugemise tulemusel ja teine klient muudab seda sama mälublokki, võib esimene klient jääda kasutama kehtetut (stale) andmekoopia, ilma et ta muutusest teaks. Vahemälu sidusus on täpselt selle probleemi haldamiseks ja järjepidevuse säilitamiseks vahemälu ning peamise mälu vahel mõeldud mehhanismide üldnimetus.

Miks see on oluline

Ilma sidususeta võivad mitme lõime või tuuma programmid lugeda vananenud väärtusi, mis viib ränki loogikavigadeni. Samuti põhjustab vahemälukoopiate erinevus täiendavat sünkroniseerimist tarkvaras (näiteks tihedad lukuoperatsioonid), mis omakorda vähendab süsteemi jõudlust. Sidus süsteem võimaldab arvutitel töötada paralleelselt, säilitades samal ajal õiged ja prognoositavad andmete väärtused.

Levinud lahendused ja protokollid

Peamised lähenemised vahemälu sidususe lahendamiseks on:

- Snooping-põhised protokollid – igas protsessori vahemälus jälgitakse (snoop) bussil toimuvat liiklust; kui üks vahemälu kirjutab mäluaadressi, teised kuulajad teavad seda ja kas uuendavad või tühistavad oma koopiad. See töötab hästi väiksema tuumade arvuga süsteemides ja jagatud bussiga arhitektuurides.

- Directory-põhised süsteemid – keskselt või jaotatud kataloog hoiab kirjet selle kohta, millised sõlmed/vahemälud omavad konkreetse mälubloki koopiat; uuendusi koordineeritakse kataloogi abil, mis vähendab kogu süsteemi liiklust ja on skaleeritavam suure hulga sõlmedega süsteemides.

- Write-invalidate vs write-update – kahe põhistrateegia erinevus: write-invalidate kustutab teiste koopiad, kui toimub kirjutus (nii et kirjutaja saab eksklusiivse õiguse), write-update aga levitab uut väärtust teistele koopiatele. Write-invalidate on enamlevinud, sest see vähendab suurt kirjutuskoormuse korral edastatava andmemahu.

Staatused ja MESI

Paljud protokollid töötlevad vahemäluregistreid olekute kaudu. Üks tuntumaid on MESI-mudel, kus iga mälublokk võib olla ühes järgmistest olekutest:

- Modified (M) – plokk on vahemälus muudetud ja erineb peamisest mälust; ainult sellel vahemälul on värske koopia.

- Exclusive (E) – vahemälal on eksklusiivne ja ühtne koopia, mis vastab peamise mälu väärtusele; teised vahemälud koopiat ei oma.

- Shared (S) – koopiad võivad eksisteerida mitmes vahemälus ja need vastavad peamise mälu väärtusele.

- Invalid (I) – vahemälus olev koopia on kehtetu.

Lisaks on laiendusi nagu MOESI, mis lisab täiendava "Owned" oleku, et vähendada kopeerimist kirjutuste ja lugemiste ajal.

False sharing (valed jagamised)

False sharing tekib siis, kui kaks eri lõime või protsessorit kirjutavad erinevatele mälavaldkondadele, mis asuvad samas vahemälujoones (cache line). Kuigi loogiliselt neid andmeid ei jagata, põhjustab ühise vahemälujoone muutumine sidususe tõttu pidevaid invalideerimisi ja ülekandeid, mis tugevalt halvendab jõudlust. Selle vältimiseks tuleks andmete paiknemist mäluplokis planeerida (näiteks struktuuride täitmine või pustalised joondused).

Vahemälu sidusus vs mälu järjepidevus (consistency)

Oluline on eristada mõisteid: sidusus tagab, et iga üksiku mäluaadressi koopiad on kooskõlas; järjepidevus (memory consistency) aga määrab reeglid, kuidas mitme aadressi operatsioonide nähtavus ja järjekord rakendustele avalduvad. Sidusus on seega järjepidevuse erijuht, kuid järjepidevusmudelid (nagu sequential consistency, release consistency jt) määravad rangemaid või leebemaid nähtavuse ja järjestuse nõudeid.

Jõudlus ja skaleeruvus

Vahemälu sidusus lisab süsteemile ülepea ja liiklust (invalideerimised, uuendused, päringud kataloogile), mis võib mõjutada latentsust ja läbilaskevõimet. Snooping töötab hästi väikese või keskmise suurusega süsteemide puhul, kuid suures mastaabis on directory-põhised lahendused tõhusamad. Tarkvara ja algoritmide kujundamisel tuleb arvestada sidususe tegevust mõjutavaid tegureid (nt false sharing, sünkroniseerimiskulud).

Praktilised soovitused arendajale

- Katilda andmete paiknemine: väldi selliseid andmestruktuure, mis panevad tihti kirjutatavad väljad samasse vahemälujoone.

- Kasutage sobivaid sünkroniseerimismehhanisme (lukud, atomaaroperatsioonid, barjäärid) ning vähendage liigset sünkroonimist.

- Testa ja profiileeri rakendust mitmetuumalises keskkonnas, et tuvastada false sharingut ja koormuse tippe.

Kokkuvõttes on vahemälu sidusus kriitiline osa kaasaegsete mitmetuumaliste ja jaotatud süsteemide arhitektuurist: see tagab andmete õigsuse, kuid nõuab hoolikat protokollide ja tarkvaralise disaini valikut, et säilitada head jõudlusnäitajad.