Superskalaarse protsessori konstruktsioon võimaldab ühe protsessori tuumas saavutada käsu-tasandi paralleelsuse, mis tähendab, et sama taktimäära juures saab protsessor teha rohkem tööd. Tegemist on arhitektuuriga, kus protsessor suudab ühe taktsükli jooksul täita rohkem kui ühe käsu — seda saavutatakse käskude samaaegse käivitamise jaotamise (nn käskude jaotamine) kaudu duplikaatsetele funktsionaalsetele üksustele. Iga funktsionaalne üksus on protsessori südamikus asuv täitmisressurss, nagu aritmeetiline loogikaüksus (ALU), ujukomaarvutusüksus (FPU), bitišifter või korrutisüksus.

Määratlus ja eristus

Superskalaarne protsessor on skaalarprotsessori laiendus: iga käsk ikkagi töötleb tavaliselt ühte andmeühikut, kuid protsessori tuumas on mitu duplikaatset funktsionaalset üksust, nii et mitu sõltumatut käsku saavad käia paralleelselt. See erineb vektorprotsessorist (kus üks käsk töötleb korraga paljusid andmeelemente) ja VLIW-i (Very Long Instruction Word), kus paralleelsus määratakse kompilaatori tasemel staatiliselt. Superskalaarsus on dünaamiline: riistvara tuvastab ja käivitab paralleelselt täidetavad juhised jooksvalt.

Tööpõhimõte — kuidas superskalaarsus saavutatakse

Superskalaarset tehnikat toetavad mitu tuuma omadust ja tööetappi:

- Juhised pärinevad järjestatud juhiste nimekirjast (programmi järjekord).

- Protsessori riistvara suudab välja selgitada andmesõltuvused käskude vahel (kes sõltub kelle tulemusest).

- Protsessor suudab lugeda ja dekodeerida mitu käsku ühe taktitsükli kohta ja otsustada, millised neist saab samaaegselt välja saata (issue) ja täita (execute).

Superskalaarses seadistuses vastutab käskude saatja (dispatcher/issue logic) käskude lugemise ja analüüsi eest ning otsustab, millised käsud suunatakse millisele funktsionaalsele üksusele. Kui riistvara tuvastab sõltumatud käsud, saab ta need paralleelselt välja saata ning täitmine võib toimuda samaaegselt.

Olulised komponendid ja mehhanismid

- Funktsionaalsed üksused: mitut ALU-d, FPU-sid, loogika- ja liitmisüksusi, mis võimaldavad paralleelset täitmist (palju sõltub disainist; tüüpiliselt võib tänapäevane protsessor omada mitut ALU-d, mitut FPU-d ja SIMD-üksusi).

- Käskude saatja ja planeerija: loeb, dekodeerib ja otsustab, millised käsud välja anda või edasi lükata.

- Riistvaraline dünaamiline ajastamine (dynamic scheduling): võimaldab välja anda käske väljaspool algset järjestust, säilitades programmi nähtava järjekorra abil korrektse tulemuse (näiteks Tomasulo algoritm, register renaming).

- Registerite ümbernimetamine (register renaming): kõrvaldab kirjutamise/järjestussõltuvusi (WAW ja WAR) ja lubab laialdasemat paralleelsust.

- Hargnemise ennustamine (branch prediction) ja spekulatiivne täitmine: minimeerivad kontroll-sõltuvuste (branch) tõttu tekkinud ooteaegu.

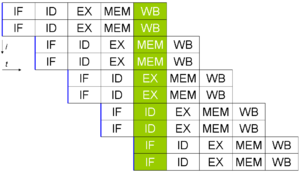

- Pipelining: enamik superskalaarsetest protsessoritest on ka torustikuga (pipeline), kus iga käsk läbib mitu täitmisetappi; see suurendab läbivoolu (throughput) kombineeritult superskalaarsusega.

Eelised

Superskalaarne disain pakub mitmeid praktilisi eeliseid:

- Suurem jõudlus ( kõrgem IPC — instructions per cycle), sest protsessor täidab samal ajal mitut käsku.

- Hea jõudluse kasv ilma sagedust tõstmata — st sama takti juures rohkem tehtud tööd.

- Paindlikkus: dünaamiline ajastamine ja riistvaraline paralleliseerimine võimaldavad realiseerida juhise-tasandi paralleelsust ilma kompilaatori keerukate transformatsioonideta.

- Üldotstarbelised protsessorid on muutunud laialdaselt superskalaarseks — alates 2000. aastatest kõik suuremad töölauaprotsessorid kasutavad erineva astmega superskalaarsust ning alates 2008. aastast on see praktiliselt standard paljudes üldotstarbelistes protsessorites. Tüüpiline kaasaegne superskalaarne protsessor võib sisaldada näiteks kuni 4 ALU-d, 2 FPU-d ja mitmeid SIMD-üksusi.

Piirangud ja probleemid

Superskalaarsus ei garanteeri lõpmatut kiirendust — selle efektiivsus sõltub juhistevahelisest sõltuvusest ja muust riistvara piirangustest:

- Andmesõltuvused (RAW, WAR, WAW) piiravad, kui palju käske saab tõepoolest samaaegselt täita.

- Struktuursed konfliktid: kui mitu käsku nõuavad samaaegselt sama funktsionaalset üksust (nt ainult üks adder saadaval), tekib kitsaskoht.

- Käskude toomise ja dekodeerimise kitsaskohad: käskude tõmbamine ja dekodeerimine peab toimuma piisava laiusega (fetch/decoder bandwidth), muidu ei saa dispetšer piisavalt tööd pakkuda.

- Hargnemised ja spekulatsioon: ebatäpsed hargnemise ennustused ja spekulatiivse täitmise tagasiheit võivad põhjustada suure hulga tühikäike ja ajakadu.

- Skaleerimise keerukus: laiema superskalaarsuse toetamine (nt 8+ issue width) suurendab riistvara keerukust ja energiatarvet, ning kasulik IPC kasv kipub hääbuma tänu kasvavale sõltuvusele juhistest ja piiratud paralleelsusele.

Tehnilised meetodid piirangute ületamiseks

Selleks, et hoida funktsionaalsed üksused hõivatuna ja suurendada efektiivset paralleelsust, kasutatakse mitmeid tehnikaid:

- Riistvaraline register renaming — eemaldab kunstlikud sõltuvused.

- Dünaamiline ajastamine (out-of-order execution) — võimaldab välja anda käske väljaspool algset järjestust, asetades ettepoole sõltumatuid käske.

- Tõhus branch prediction ja spekulatiivne täitmine — vähendavad kontrolliga seotud latentsust.

- Suurem ja parem käskude eeltoomine (pre-fetch), mitmekanaliline instruktsioonivahemälu ja kiirem dekodeerimine.

Võrdlus teiste meetoditega

Superskalaarsus erineb mujalt tulevast paralleelsusest:

- VLIW (Very Long Instruction Word) usaldub paralleelsuse määramisel kompilaatorile, superskalaarsus teostab selle dünaamiliselt riistvaras.

- SMT (Simultaneous Multithreading) laseb eri niitidel (threads) kasutada samaaegselt samu funktsionaalseid üksusi; superskalaarsus keskendub ühe niidi sees juhiste paralleelsusele.

- Vektor- ja GPU-arhitektuurid töötlevad massiivset andmeparalleelsust samaaegselt, superskalaarsus on optimeeritud juhise-tasandi (instruction-level) paralleelsusele üldotstarbeliste programmide jaoks.

Praktilised näited ja ajalooline kontekst

Paljud tuntud protsessorid on kasutanud superskalaarsust: varasemad x86 disainid (nt Intel Pentium Pro/II/III ja hiljem Core-seeria), AMD protsessorid, samuti kaasaegsed ARM Cortex-A tuumad. Superskalaarsed disainid on arenenud koos torustiku-, hüpoteetilise täitmise ja branch-prediction tehnoloogiatega, mis võimaldasid üldjuhul märgatavat IPC kasvu võrreldes lihtsamate skalaarsete protsessoritega.

Kokkuvõte

Superskalaarne arhitektuur on võimas meetod, et tõsta protsessori jõudlust ilma ainult taktsagedust suurendamata. Selle edu sõltub riistvara võimest tuvastada ja käitada paralleelselt sõltumatuid juhiseid ning hoida mitu funktsionaalset üksust efektiivselt hõivatuna. Kuigi superskalaarne disain on tänapäevastes üldotstarbelistes protsessorites laialt levinud, piiravad selle kasu andmesõltuvused, struktuursed konfliktid ja tõrked käskude toomises/ennustamises — seetõttu kasutatakse kombineeritult mitmeid täiustusi (register renaming, out-of-order execution, branch prediction jne).